August 15, 2023 – In a recent video, the YouTube channel “Moore’s Law Is Dead” has shed light on new revelations about AMD’s upcoming flagship graphics card under the RDNA4 architecture. The latest insights suggest a departure from previous plans, as AMD has reportedly scrapped all release plans for the Navi41 and Navi42 models.

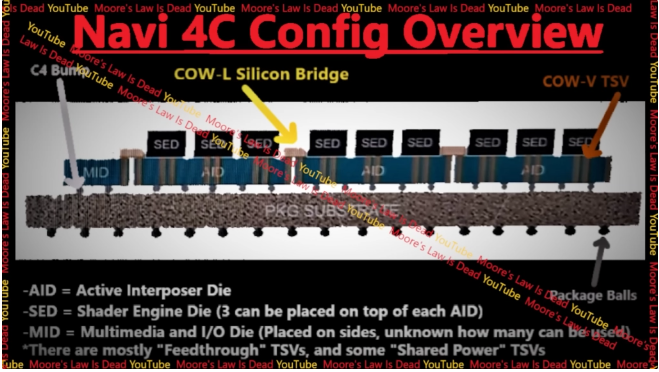

Leaked images showcase a glimpse of the Navi4C series, hinting at remarkable advancements compared to the RDNA3 lineup. The Navi4C series is rumored to feature a trio of bare dies, namely AIDs, SEDs, and MID, arranged innovatively on a single package.

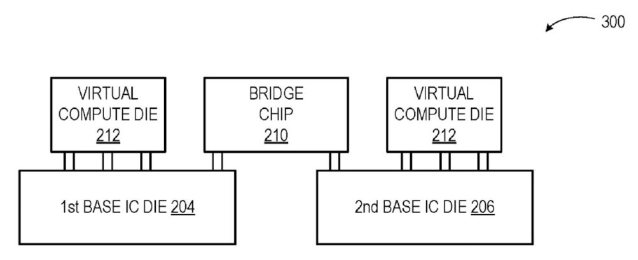

According to the channel, the Navi4C design introduces at least 3 active interposers on a single packaging layer. These interposers play a crucial role in routing data between the topmost bare dies. This innovative approach is underpinned by a cutting-edge 3D architecture, indicating a significant departure from the RDNA3 configuration.

Notably, each active interposer is host to 3 Shader Engine Dies (SEDs), resulting in a total of 9 SEDs within the structure. This enhancement is poised to substantially elevate the graphics processing prowess of the Navi4C series. Positioned on the left side of the architecture, an additional Multimedia and I/O Die (MID) further underscores the commitment to bolstering multimedia capabilities and I/O functionalities.

Intriguingly, plans for RDNA4 include the integration of Infinity Cache and memory controller chiplets. While RDNA3 housed 7 chiplets, the upcoming RDNA4 architecture is poised to elevate this number to an impressive range of 13 to 20 chiplets. This strategic decision speaks to AMD’s focus on maximizing performance efficiency and data throughput.

The leaked report also ventures into AMD’s projected timeline. It anticipates the release of the Navi44 model in mid-2024, anticipated to be fabricated on the 6nm process node. Subsequently, the Navi43 model is predicted to debut in 2025, harnessing the advancements of the 3nm process node. This leap in miniaturization is expected to accommodate a higher density of Compute Units (CUs) within a smaller form factor.

It’s important to note that while these insights provide an intriguing glimpse into AMD’s plans, they stem from unofficial sources. For the most accurate and up-to-date information, it is advisable to refer to official announcements from AMD. As the technological landscape continues to evolve, these leaked details might witness modifications before the eventual launch.