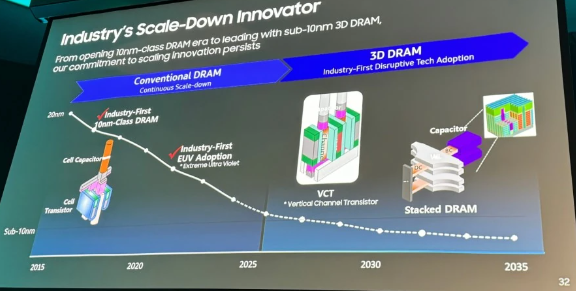

April 01, 2024 – According to a report by Semiconductor Engineering, Samsung Electronics has announced its plans to lead the industry into the 3D DRAM memory era after 2025, as revealed at the recent Memcon 2024 conference.

The DRAM memory industry is facing a challenge as it approaches the later part of this decade, with the line width shrinking below 10nm. At such fine scales, existing design solutions are becoming increasingly difficult to scale further, prompting the exploration of innovative memory designs, including 3D DRAM.

During its presentation at Memcon 2024, Samsung showcased two new 3D DRAM memory technologies: Vertical Channel Transistor and Stacked DRAM.

Unlike traditional transistor structures, Vertical Channel Transistors orient the channel vertically instead of horizontally, significantly reducing device footprint while demanding higher precision in etching processes.

Meanwhile, Stacked DRAM takes advantage of the z-direction space, accommodating more memory cells in a smaller area, increasing single-chip capacity to over 100G compared to existing 2D DRAM structures.

The 3D DRAM market is expected to reach $100 billion by 2028, equivalent to approximately 724 billion Chinese yuan at current exchange rates. To compete with other major memory manufacturers, Samsung has opened a new 3D DRAM research and development laboratory in Silicon Valley earlier this year.

This significant investment by Samsung underscores the growing importance of 3D DRAM technology in meeting the increasing demand for high-capacity memory solutions in various computing applications. With its innovative approach, Samsung aims to maintain its leadership position in the global memory market and pave the way for the next generation of memory technologies.