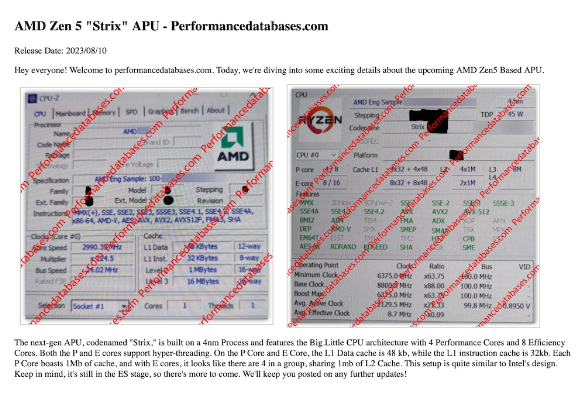

August 10, 2023 – In a surprising revelation today, the website “PerformanceDatabases” has unveiled a trove of new information regarding AMD’s next-generation mobile processors, code-named “Strix.” This unveiling comes in the form of a detailed presentation showcasing the prowess of the upcoming AMD “Strix” processors through the lens of CPUz and Hwinfo software.

The heart of the innovation lies in the architecture of the “Strix” processors. The concept of a “big.LITTLE” design takes center stage, with an impressive arrangement of 4 high-performance cores and 8 efficiency cores. Termed as the Performance (P) cores and Efficiency (E) cores respectively, each of these cores boasts the added advantage of hyper-threading capabilities, ensuring a substantial boost in multitasking potential.

A deeper dive into the technical specifications reveals an intriguing cache configuration. While each P core enjoys the luxury of a dedicated 1MB L2 cache, the E cores adopt a distinctive approach. Arranged in clusters of 4, every cluster collectively shares a 1MB L2 cache. This strategic distribution promises to expedite data retrieval and further enhance the overall computational efficiency.

The AMD “Strix” processors are presently in the Engineering Sample (ES) stage, indicating an ongoing process of refinement and optimization before they make their official debut. This behind-the-scenes peek showcases AMD’s dedication to delivering cutting-edge technology that is primed for peak performance.

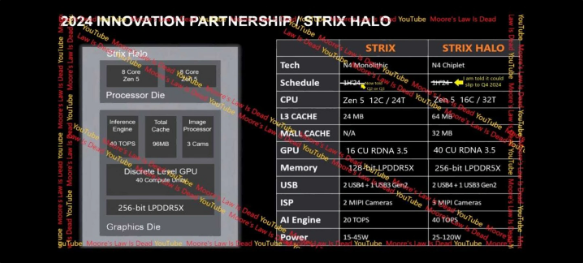

Coinciding with this revelation, renowned international blogger “Moor’s Law Is Dead” had previously hinted at similar details. According to their sources, the upcoming 12-core APU from AMD, aptly named “Strix,” is set to harness the power of N4 fabrication technology. The intricacies of the design reveal a monolithic chip structure, integrating all components seamlessly into a single unit.

The graphics prowess of the “Strix” APU receives a notable boost, with 16 Compute Units (CUs) gracing its architecture. This enhancement promises a visual experience that transcends the boundaries of conventional integrated graphics.

While the official release remains in the future, the industry anticipates the “Strix” APU to emerge onto the market in the second or third quarter of the upcoming year. This projection adds to the mounting excitement surrounding AMD’s strides in innovation.

Notably, AMD is not stopping there. As a part of their forward-looking strategy, they are gearing up to introduce the “Strix HALO” APU in the fourth quarter of the same year. This variant will embrace a chiplet design, accommodating an expanded roster of 16 cores. The graphics capabilities receive an even more substantial upgrade, featuring an impressive 40 CUs. With a widened memory bus of 256 bits, the “Strix HALO” APU ensures a future-ready solution for advanced computing needs, all within a power envelope ranging from 25 to 120 watts.