January 6, 2025 – Apple’s A-series smartphone processors have undergone remarkable technological evolution in recent years. Starting from the A7 chip, which utilized a 28-nanometer process in 2013, to the cutting-edge A18 Pro chip with a 3-nanometer process in 2024, Apple has achieved significant progress in core count, transistor density, and functional features. However, this advancement in manufacturing technology has also led to a substantial increase in chip production costs, posing new challenges for the tech giant.

According to a report by Ben Bajarin, CEO and Principal Analyst at Creative Strategies, the transistor count of Apple’s A-series chips has surged from 1 billion in the A7 to 20 billion in the A18 Pro. This growth is closely correlated with the expansion of chip capabilities. While the A7 featured just two high-performance cores and a four-cluster GPU, the A18 Pro boasts two high-performance cores, four efficiency cores, a 16-core neural network processor (NPU), and a six-cluster GPU. Despite this significant enhancement in functionality, the die size of the A-series chips has remained between 80 to 125 square millimeters, thanks to the increased transistor density facilitated by TSMC’s advanced manufacturing processes.

Nevertheless, the rate of transistor density improvement has noticeably slowed down in recent years. Bajarin points out that early process nodes, such as the transition from 28 nanometers to 20 nanometers and then to 16/14 nanometers, delivered significant density gains. However, the latest processes, including N5, N4P, N3B, and N3E, have shown more modest improvements. The peak of transistor density growth occurred around the A11 (N10, 10-nanometer class) and A12 (N7, 7-nanometer class) chips, with increases of 86% and 69%, respectively. Conversely, the density enhancement from the A16 to the A18 Pro has been significantly less pronounced, primarily due to the slowing down of static random-access memory (SRAM) scaling.

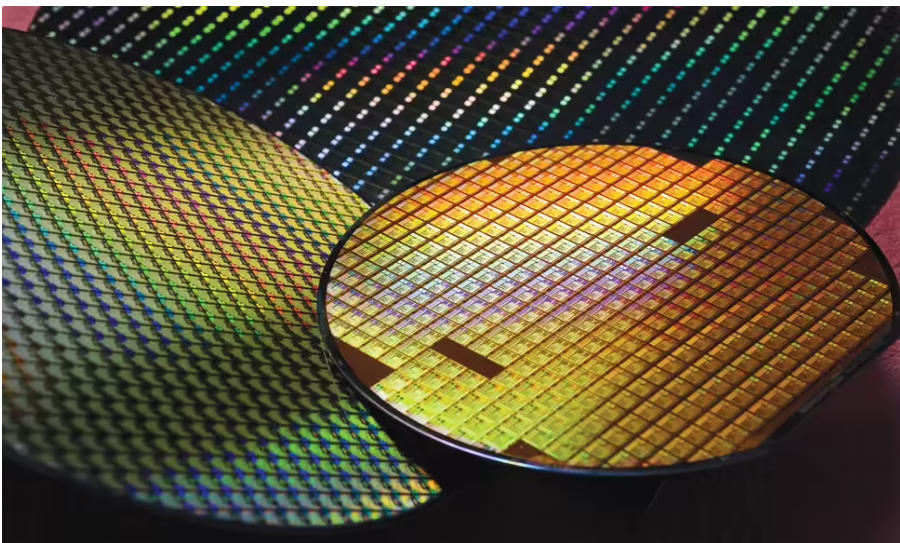

Despite the diminishing returns from technological advancements, chip manufacturing costs have escalated dramatically. Reports indicate that wafer prices have risen from 5,000fortheA7to18,000 for the A17 and A18 Pro, while the cost per square millimeter has increased from 0.07to0.25. Bajarin clarifies that these figures are sourced from third-party supply chain reports and have been validated through multiple channels, although caution is still advised when interpreting non-official information.

Apple also faces challenges in boosting chip performance. The rate of performance improvement in the A-series chips has slowed down in recent years, excluding the A18 and M4 series. This trend is primarily attributed to the increasing difficulty of enhancing instructions per clock (IPC) throughput in newer architectures. Despite these challenges, Apple has successfully maintained an improvement in energy efficiency with each generation of its products. Bajarin notes, “In the face of rising difficulties in IPC gains, Apple’s strategy of optimizing energy efficiency, even at higher costs, remains a viable approach.”

It’s worth mentioning that TSMC employs a unique business model in wafer production. Industry reports suggest that TSMC provides wafers to its clients, including both sellable and non-sellable chips, and the actual chip count depends on manufacturing yield. If the actual yield falls below the expected target by 10% to 15%, TSMC may offer financial compensation or discounts to ensure customer satisfaction. As TSMC’s primary customer for its latest manufacturing technology, Apple has the opportunity to reduce defect density by adjusting the manufacturing process, thereby improving yield and gaining an advantage in cost control. Furthermore, rumors suggest that Apple is TSMC’s only customer that pays per chip rather than per wafer, further highlighting Apple’s exceptional position in the supply chain.